マザーボードを選ぶとき、フェーズ数やVRMのスペックを気にする方も居るのではないでしょうか。このフェーズ数について、なんとなく理解はしているもののその正体は何なのか、そして多くなると何が良いのかについてはあまり触れられることはありません。

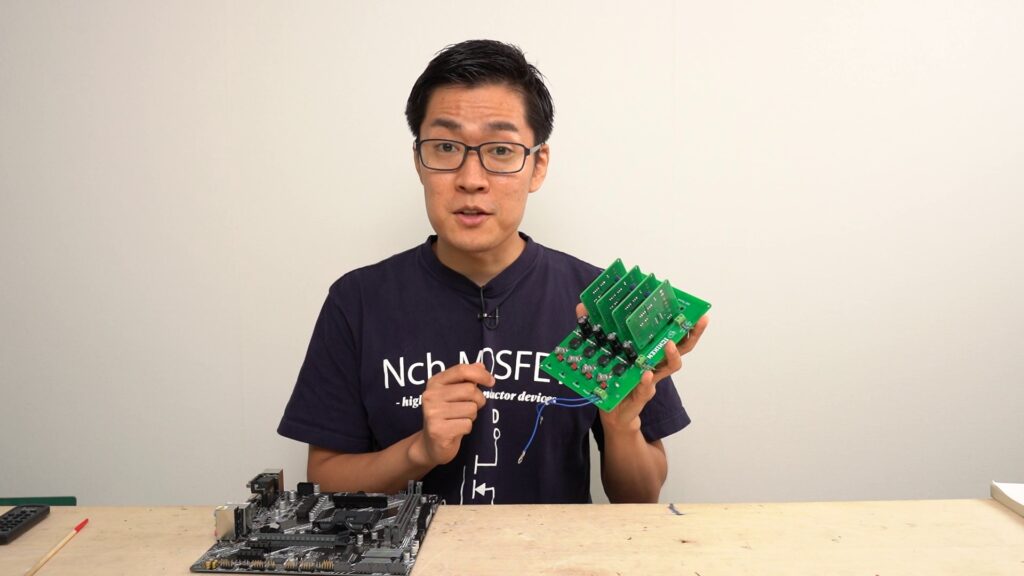

今回はこのVRMとは一体何者なのかについて、理論と実際にイチケンがVRMを自作して解説をしていきます。

なお、今回のブログ記事は元となる動画が公開されていますので、本記事以上に理解を深めたい方は是非こちらもあわせて御覧ください。

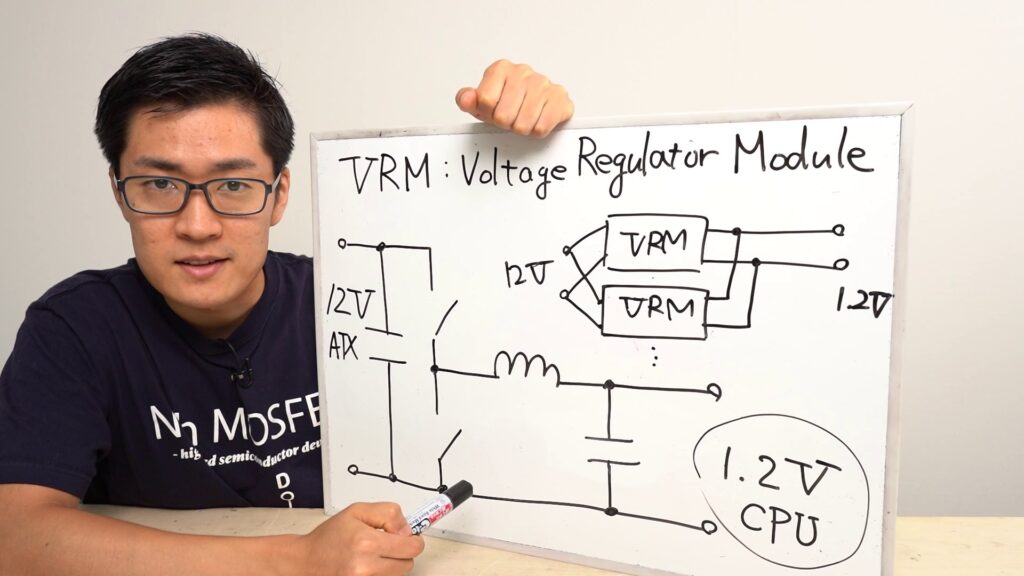

VRMについて

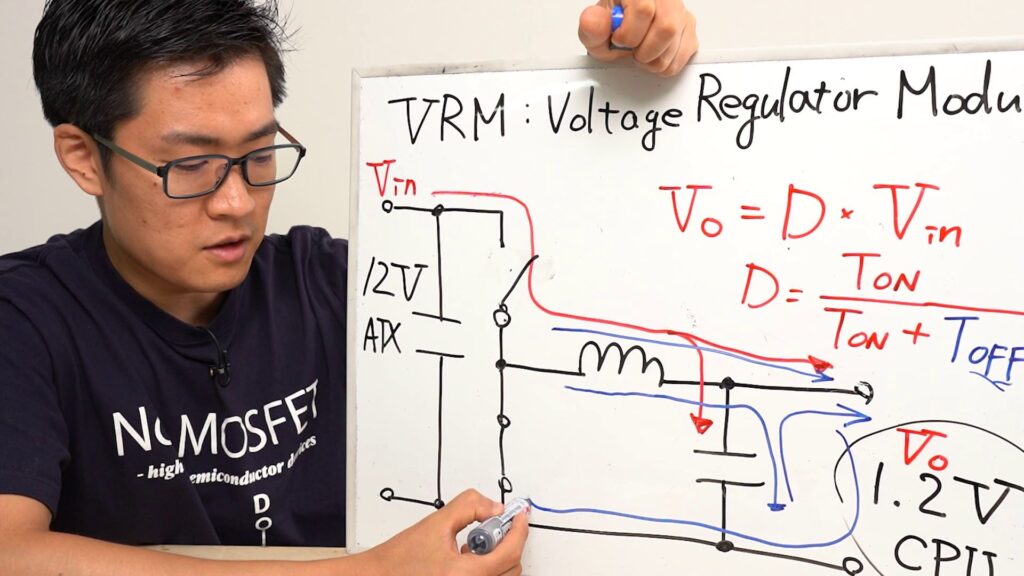

VRMについて、まず正式名称は

Voltage Regulator Module(ボルテージ レギュレーター モジュール)

といいます。頭文字を取ってVRMです。.vrmファイルではありません。

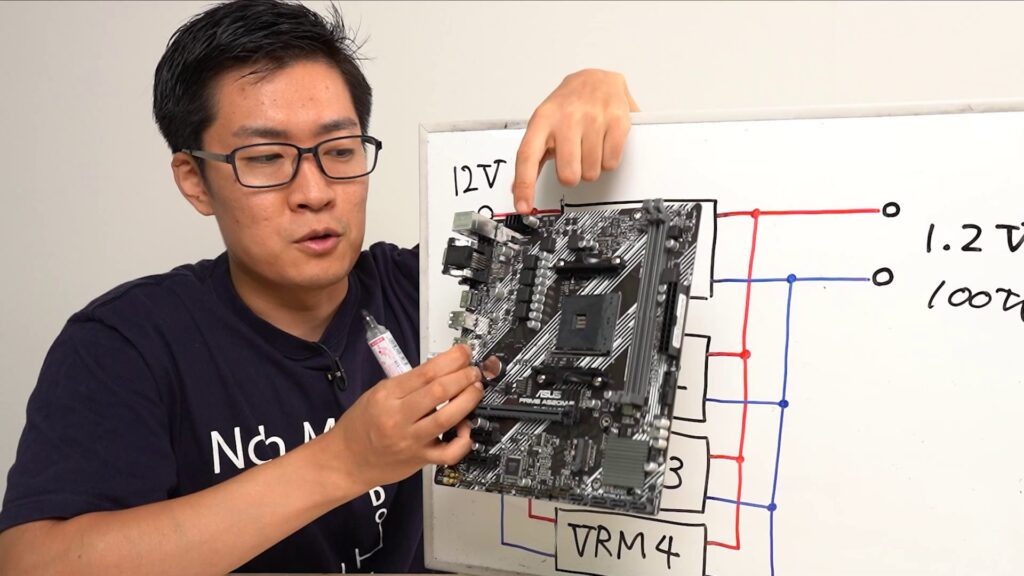

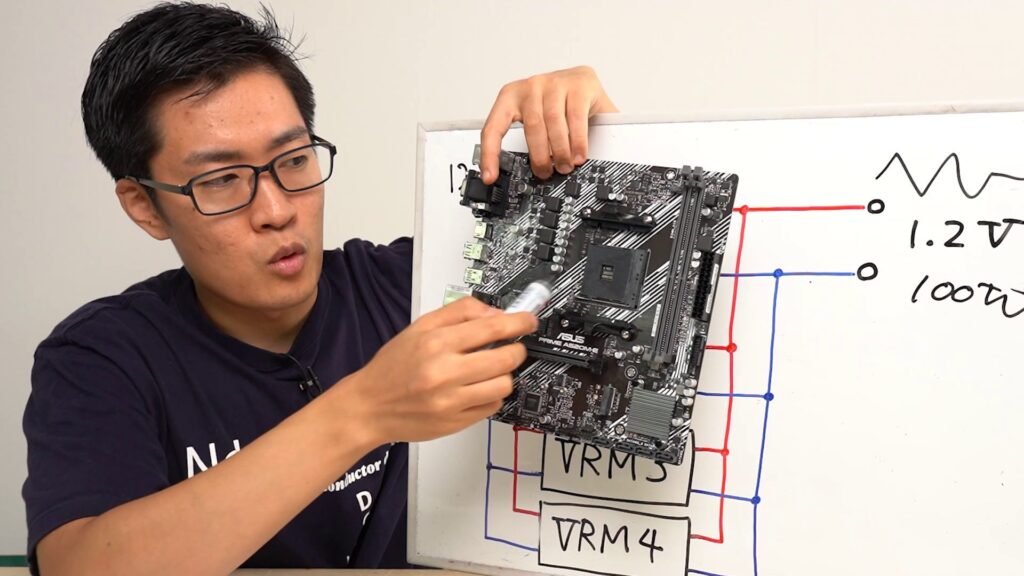

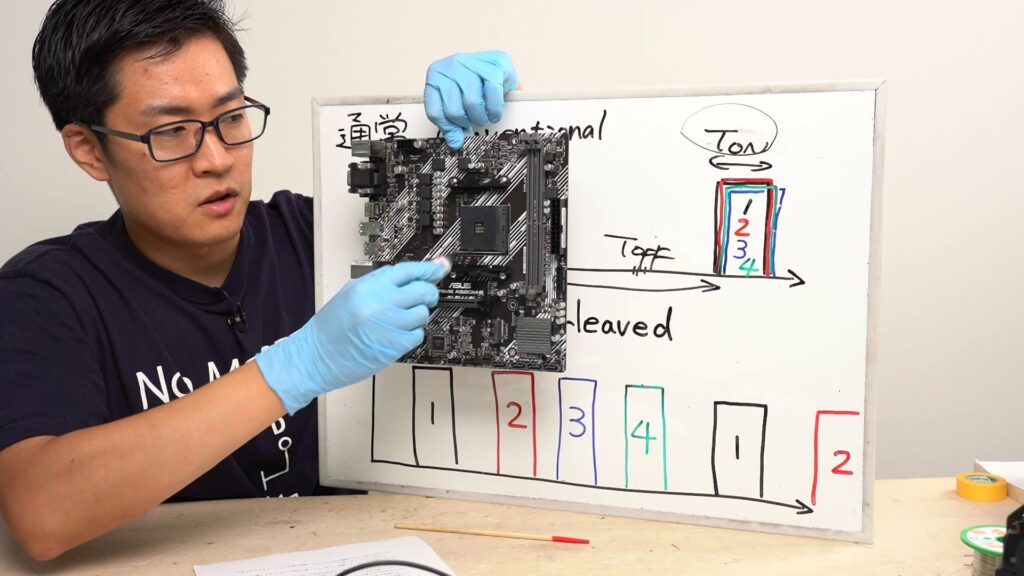

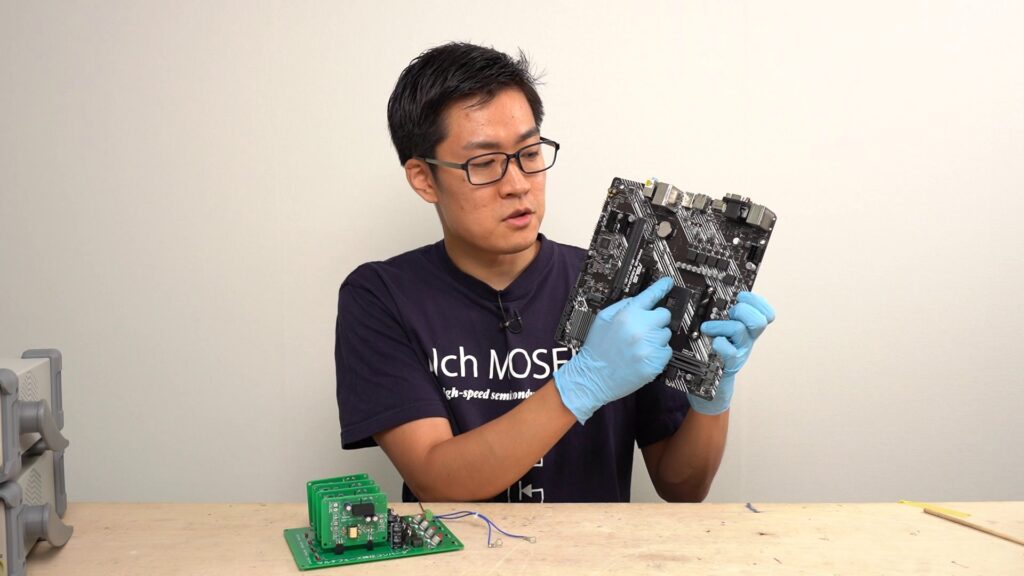

今回は解説を行うにあたり6000円程度の安価なマザーボードを一枚用意しました。ASUSの PRIME A520M-E というmicroATX規格のもので、こちらのマザーボードには6フェーズのVRMが搭載されています。

マザーボード上には実際には同じ回路が複数並列に配置されることで動作されている場合がほとんどで、その並列数のことを「フェーズ(フェーズ数)」と呼んでいるようです。近年は高消費電力のCPU対応のため、20フェーズを超える製品も登場しています。

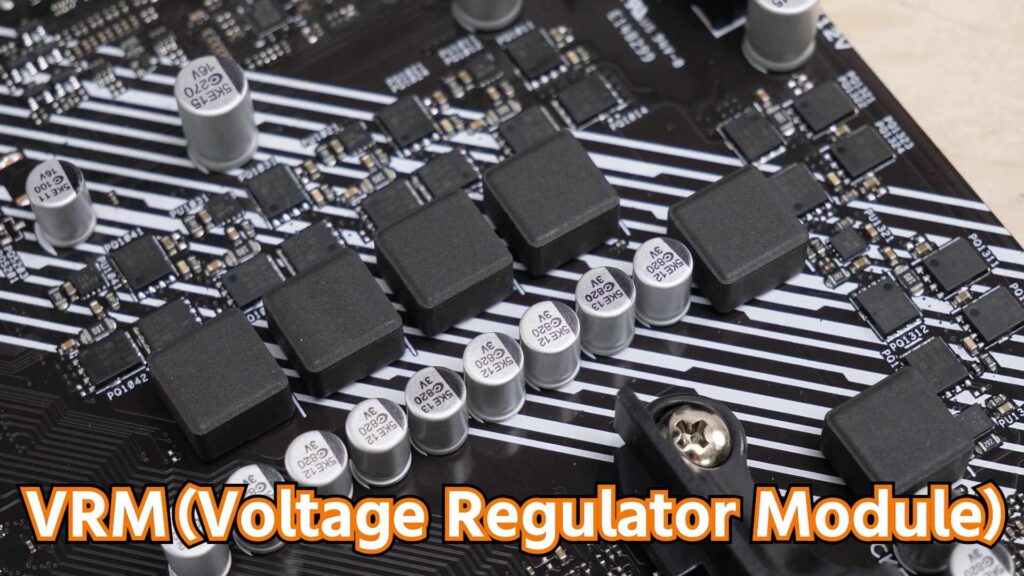

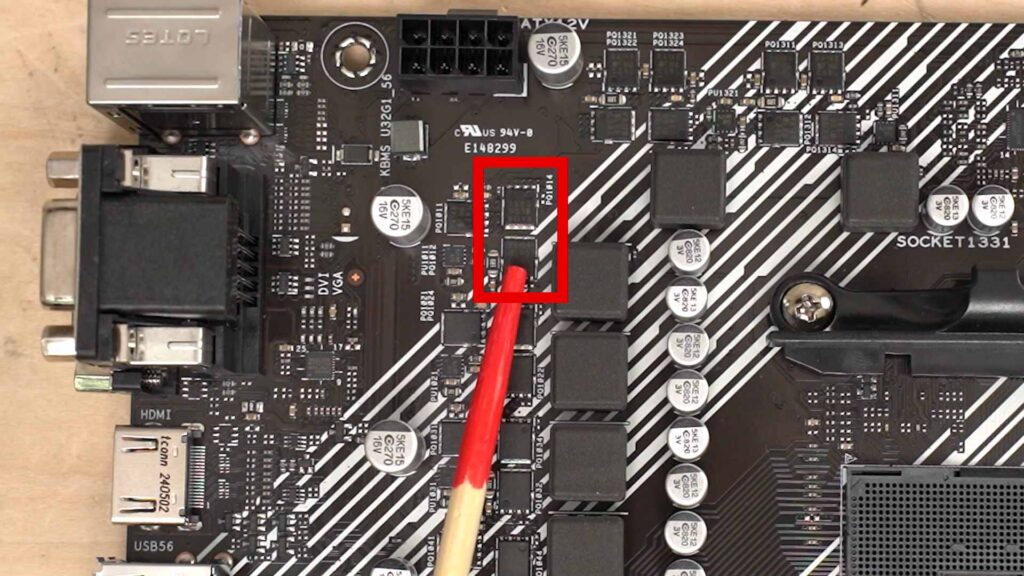

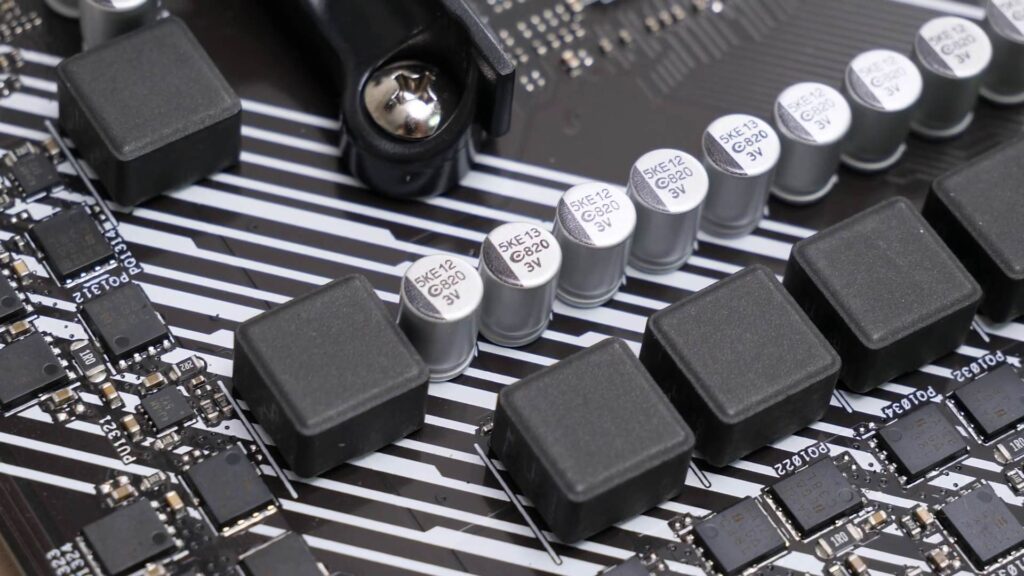

VRM回路部分をよく見てみる

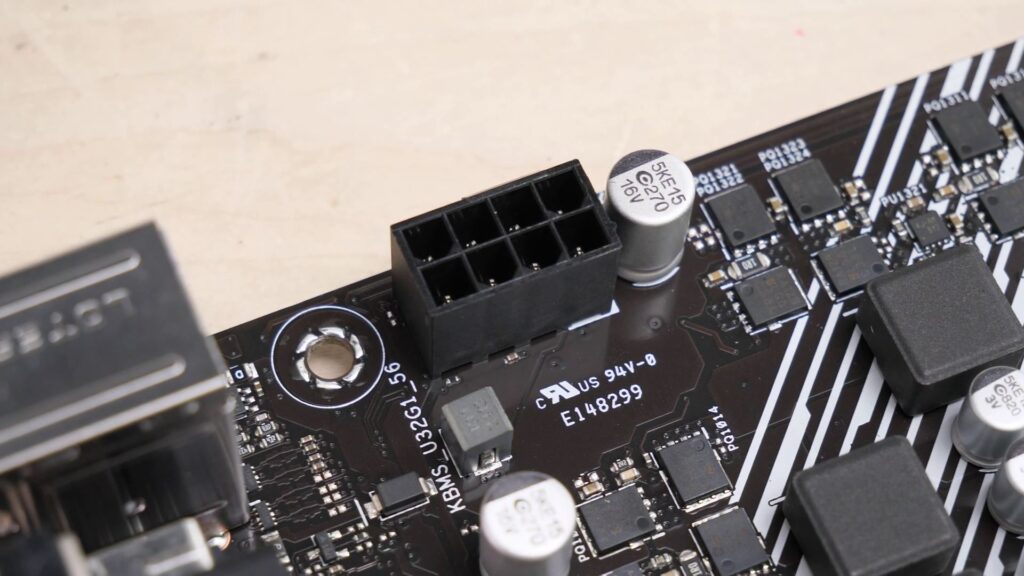

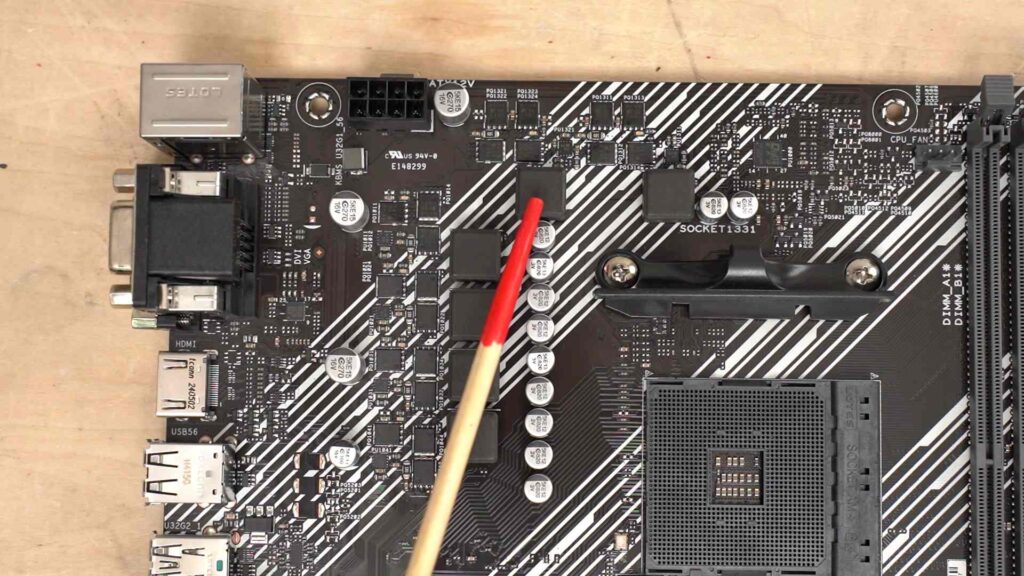

まずマザーボード上部にはATX電源からCPU用の電源供給を受けるためのコネクタが実装されています。コネクタにはATX電源からの12Vが印加されていて、これがVRM回路の入力へと入っていくことになります。余談ですがこちらのコネクタはATX規格そのものというよりEPSというサーバー用規格に源流のあるコネクタだったりするようです。

入力側には電解コンデンサが実装されており、定格は16V270uFです。主に12Vの平滑を行っているものと思われます。

VRMの1つの回路を構成している部品を見てみると、表面実装タイプのMOSFETが3つあることがわかります。このうち2つはテスターで調べたところ並列接続されているようでした。

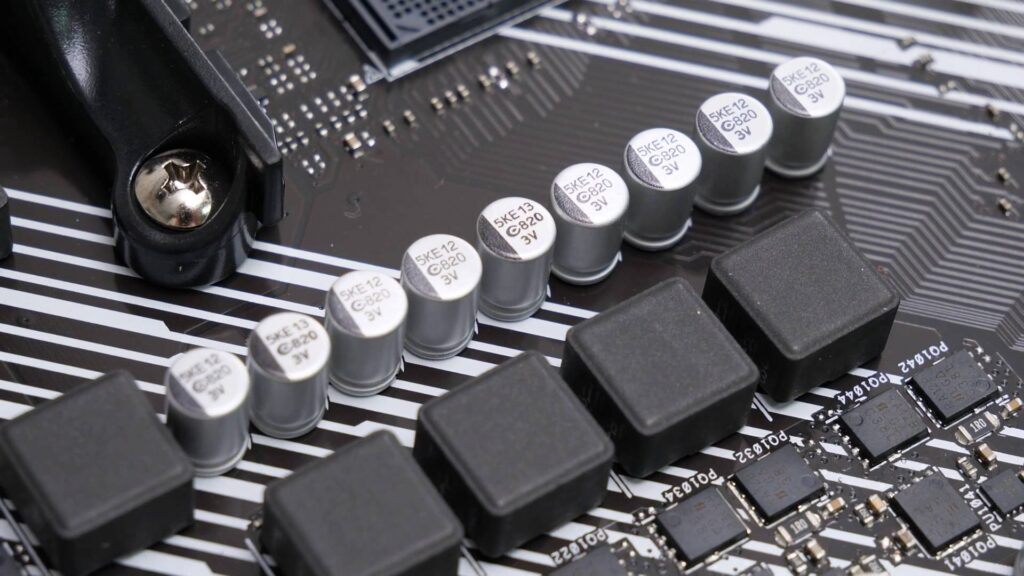

このほかにインダクタと出力側の電解コンデンサが一緒に実装されています。出力の電解コンデンサの定格はかなり低く3V820uFのものが使われていました。

CPUが動作する電圧はパフォーマンスと電力消費のバランスを取るためにかなり細かく制御されているものの、基本的には1.2V前後で動作することがほとんどかと思います。ですので出力側の部品の定格はこれに合わせる形で3V程度で十分とされているようです。

また、この部品の組み合わせと同じものが縦に4つ、マザーボード上部にもう2つほど並んでいます。合計で6フェーズです。

VRMの回路について解説

さて、ここまで実物を確認してきたわけですが、VRMの回路構成についても解説していきます。

まずざっくりとですがマザーボード上に実装されている部品を解析するとこのような構成となっています。

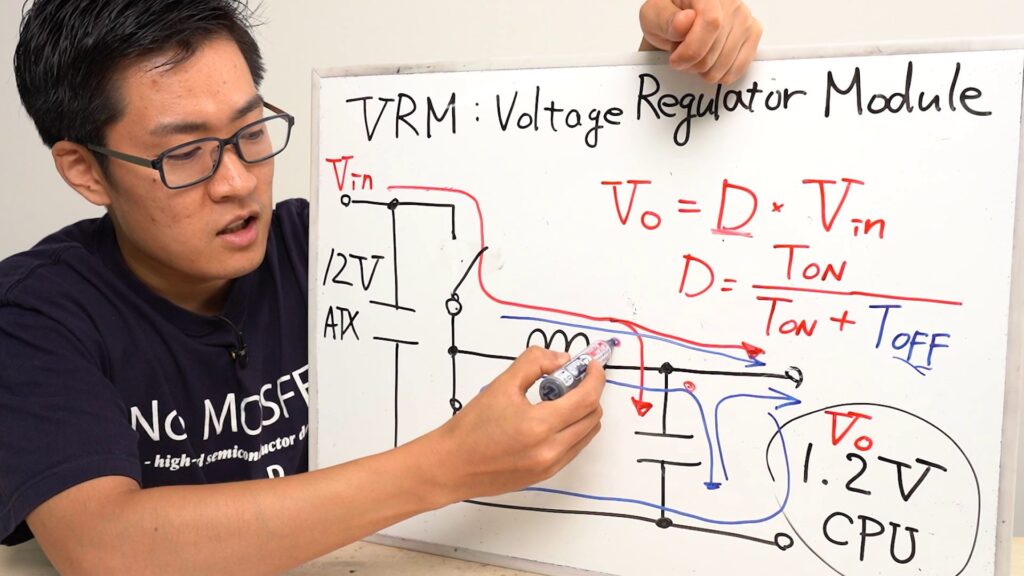

入力の電解コンデンサを通った後はMOSFETが上下に配置されており、インダクタが出力のVCCに入っています。出力のすぐ手前、GNDの間にはコンデンサが配置されているという、どうやら典型的な降圧コンバータの回路をしていることがわかりました。

VRMの役割として、ATX電源から来ている12VをCPUで使う1.2Vに降圧する事が挙げられますので、つまるところVRMの正体は降圧コンバータであり、それがいくつも並列に接続される形で電源フェーズを構成していることになります。

降圧コンバータの原理について

VRM≒降圧コンバータという構図が理解できた所で、降圧コンバータの動作原理について簡単におさらいしておきます。

なお、詳細な解説と降圧コンバータを自作する動画を以前にアップロードしていますので、こちらも是非参考にしてください。

降圧コンバータは上下に接続されたスイッチ(パワー半導体)をオン・オフすることで電圧を変換する回路です。今回参考にしたマザーボードではパワー半導体のMOSFETが使用されていました。

たとえば上のスイッチがオンしたとします。このとき電流は上側のスイッチを通ってインダクタに流れ、出力のコンデンサを充電しながら出力の負荷へと流れていきます。この上側のスイッチがオンされている時間の事をいったんT-onとします。

次に上のスイッチをオフにして、下側のスイッチをオンにします。この状態が続いている時間のことをT-offとします。

このT-offの期間では電流はどう流れるのかというと、インダクタに磁束として蓄えられたエネルギーが一定の期間二次側へと流れ続ける、ないしはキャパシタに残っている電荷が負荷へと供給される形です。インダクタの電流は負荷にも流れつつ、帰ってきた電流が下側のスイッチからループするような形の動作をします。

ここまでの説明で登場したスイッチの状態について。本解説ではパワー半導体(今回はNch-MOSFET)が以下の状態にあることを表すものとしています。

- オン → パワー半導体に電流を流せる状態

- オフ → パワー半導体に電流が流れない状態

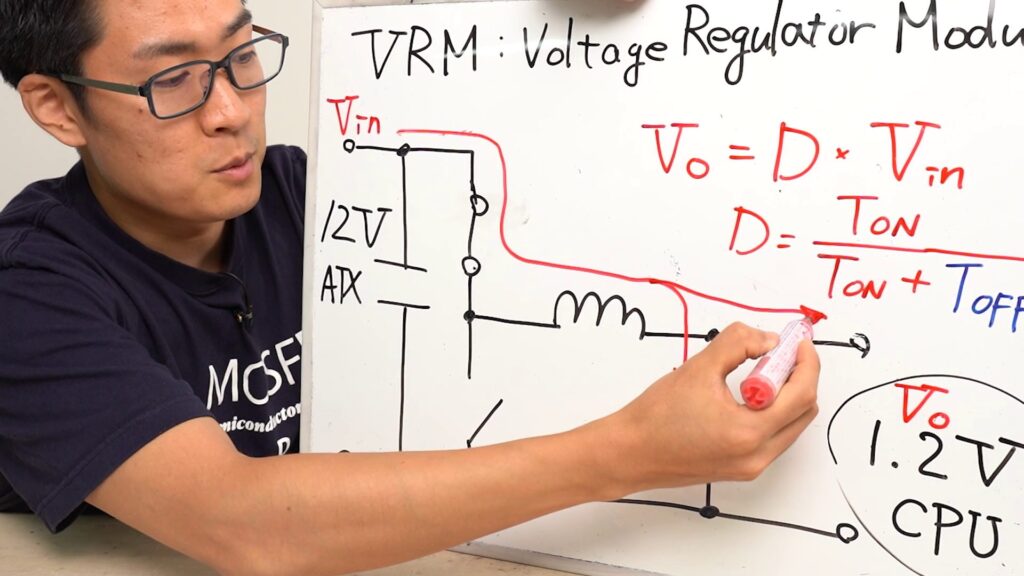

電圧変換式について

降圧コンバータの入力電圧と出力電圧の式は先程のT-onとT-offの比率「D」を用いて

$$D = \frac{\text{T-on}}{\text{T-on} + \text{T-off}}$$

のように表すことができます。今回のマザーボードの例を上げると、入力電圧の12VをCPUで使う1.2Vまで落とすことになりますのでDが0.1となるような設定が必要です。

実際の動作でどうなるのかというと、全体の動作時間(の1サイクル)あたり、10%の時間が上のスイッチが閉じて一次側から電流が供給されるT-onの状態。のこりの90%の時間はスイッチが開いて電流の供給がないT-offの時間にするということです。

このT-offの期間どこからエネルギー供給がされているかというと、回路後段のインダクタとキャパシタに蓄えられたエネルギーを使用して、CPUへエネルギーが供給されている状態となるわけです。

マルチフェーズ化のメリットとデメリット

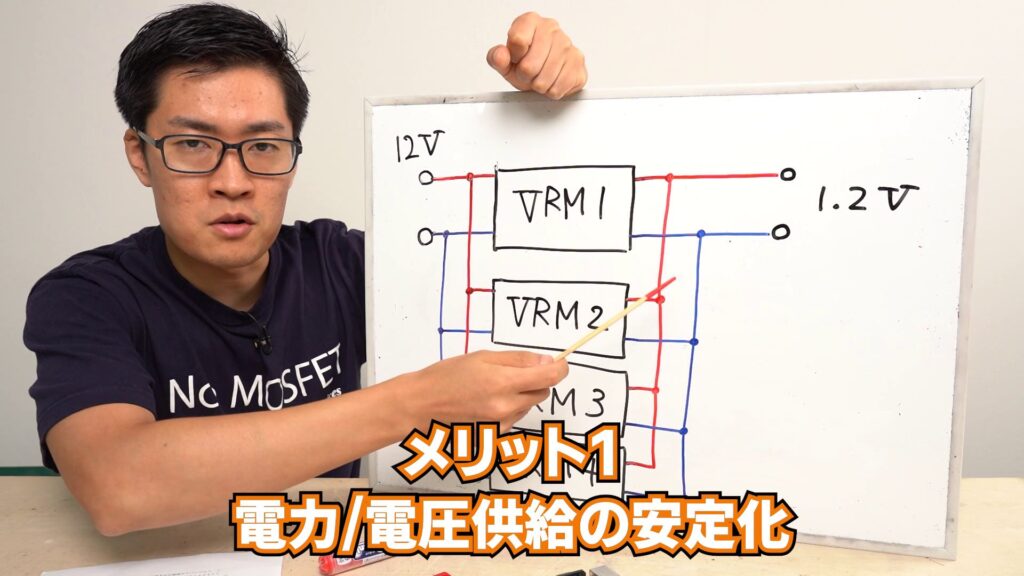

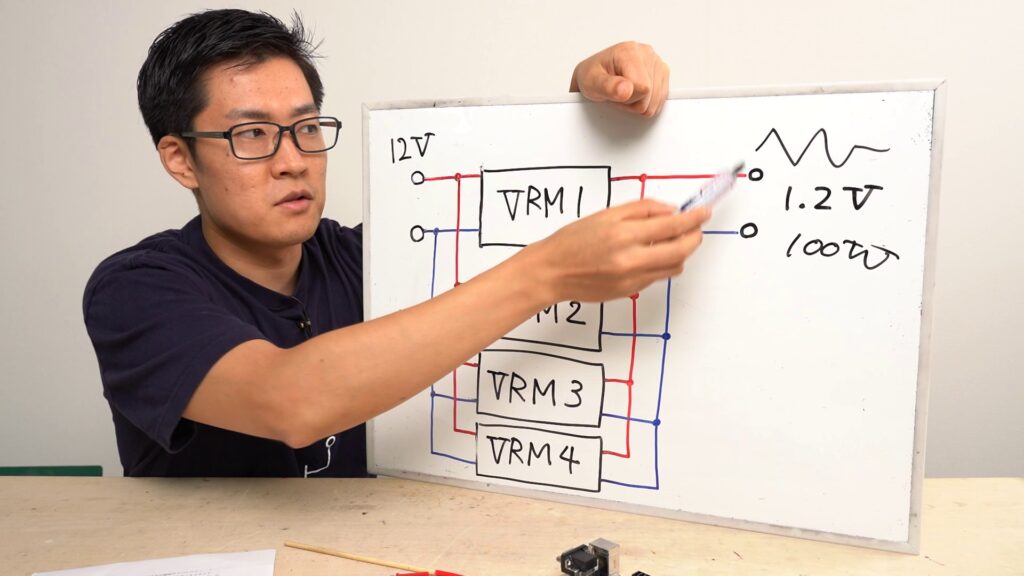

今回参考用に用意したマザーボードでは6フェーズのVRMの並列化がされていましたが、そういったマルチフェーズのマザーボードを作ることのメリットとデメリットについても触れてみたいと思います。

メリットその1

まず挙げられるマルチフェーズ化のメリットについてですが、「CPUに安定した電圧を供給する事ができる」というものです。

CPUが駆動する上で安定した電圧を供給することは欠かすことができません。たとえば計算負荷がかかってCPUの要求する電力が急激に変動したとしても、できる限り電圧変動の少ない決められた電圧(今回はすべて1.2Vで想定)を供給するという事がとても重要です。

また、マルチフェーズ化することで出力の電圧リプルを少なくする→さらに品質の良い電圧を供給できるということも、マルチフェーズ化のメリットといいますか主目的の一つです。

電圧リプルを少なくするにはマルチフェーズ化だけではなく制御方式も重要になってきますので、後ほど実験を交えながらそのあたりについてももっと掘り下げます。

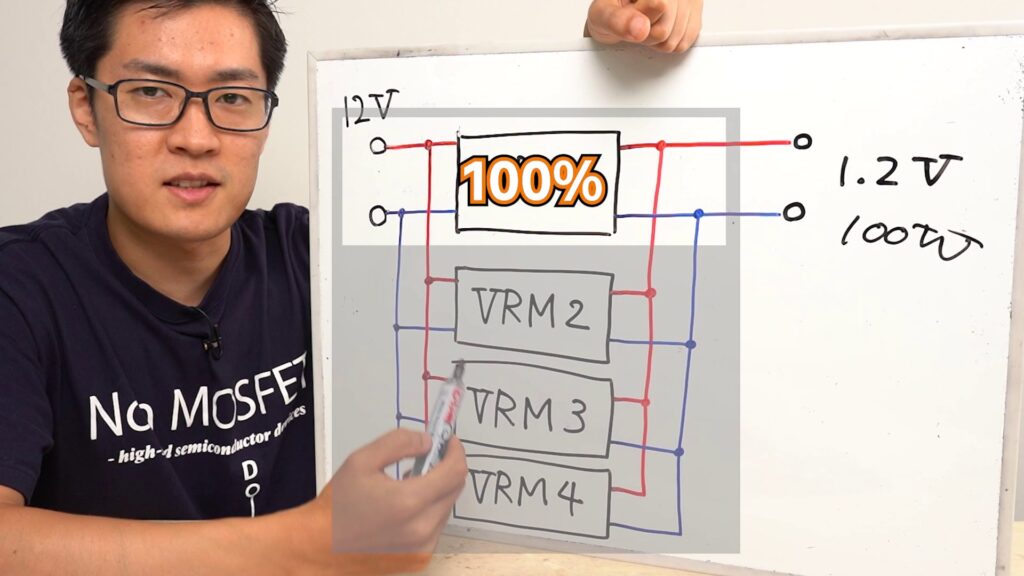

メリットその2

そしてメリット2つ目、フェーズ数が多いほど大電力を扱えるようになります。

例として100Wを消費するCPUを駆動しなければいけいない場合を想定してみます。このときフェーズが1つだけだとすると100Wすべてを一組の部品で負担しなければならず、その負荷や発熱がひどいことになるのは想像に難しくありません。

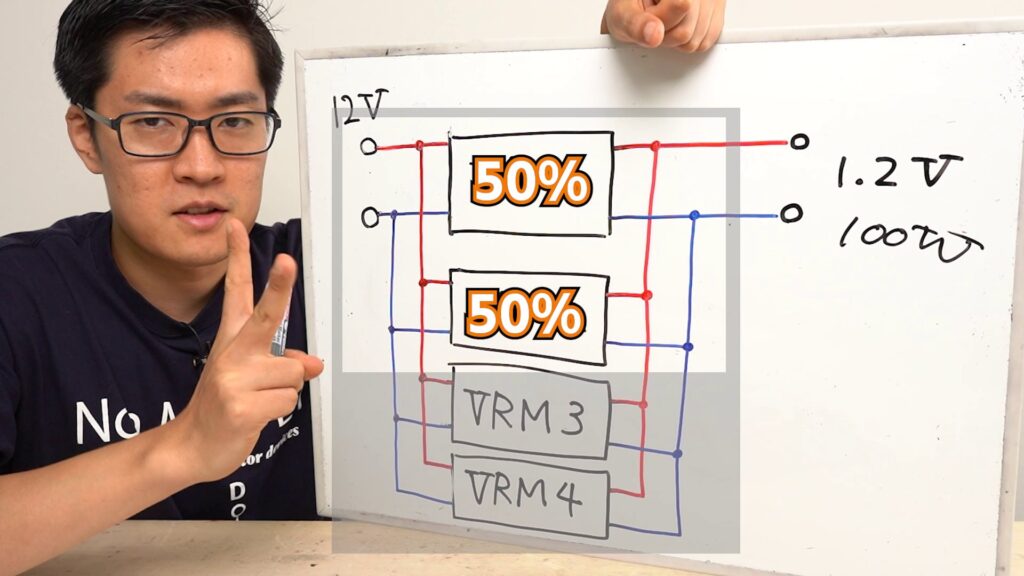

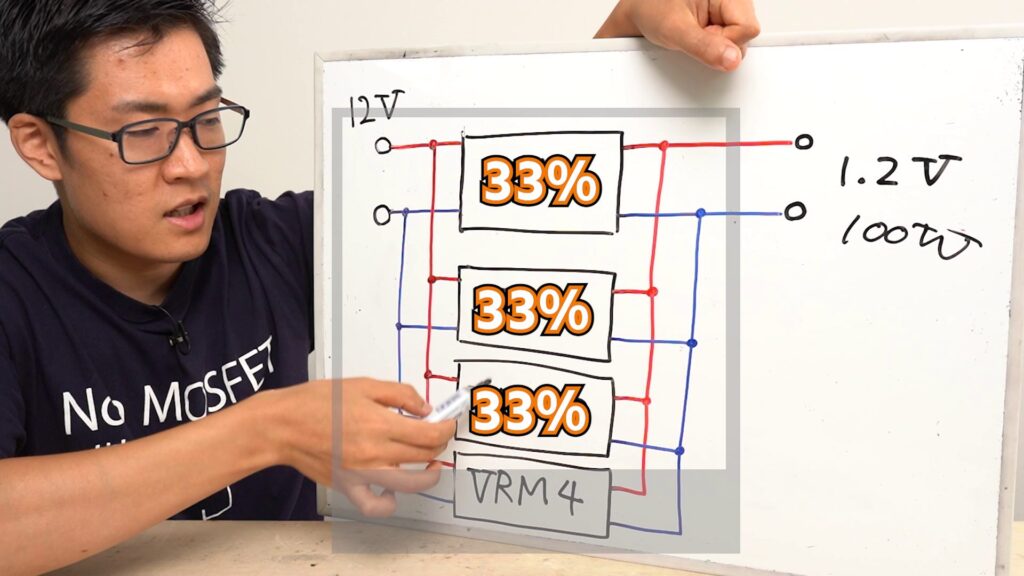

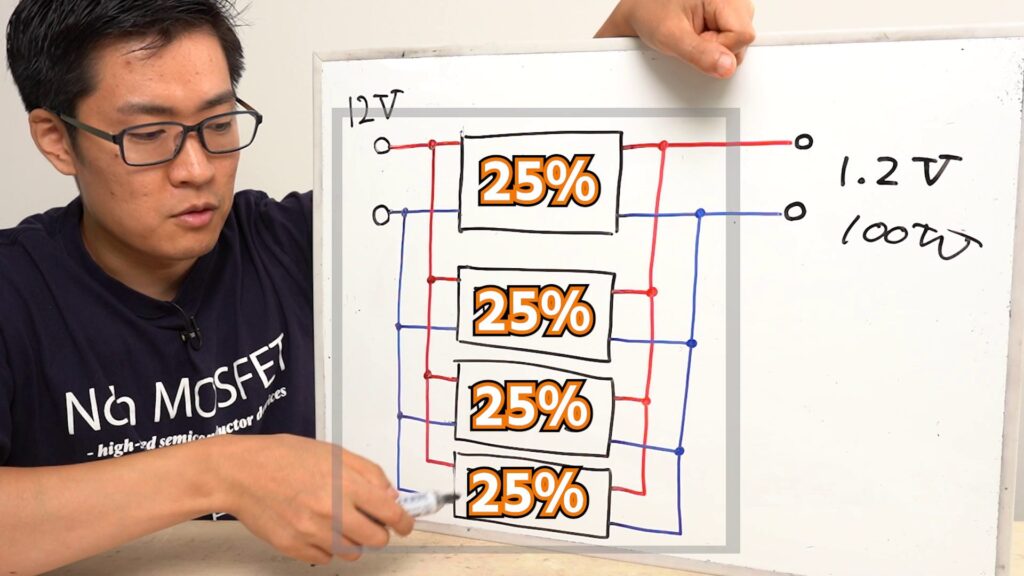

では電源フェーズが2つになるとどうなるのか

このときはそれぞれのVRM回路が100Wに対して50%、つまり50Wを負担すれば良いことになりますので、先程の半分の負荷でよくなります。

同時に3つの場合では33%、4つだと25%、さらに10フェーズを超えると全体に対しての割合は10%を下回ります。負荷が減ればそれだけ発熱が減るということで基板や部品の放熱設計もかなり楽になりますし、なによりも寿命の長期化を狙うことができます。

電解コンデンサを筆頭に、だいたいの電子部品は温度が高ければ高いほど寿命が急速に短くなります。特にマザーボードといった長時間安定して駆動することを求められる製品においては温度を下げることはとても重要です。

もちろん一定の電力に対する放熱が楽になるということは、もっと大電力を要求する負荷(CPU)に対応できるということでもありますので、上位のCPU、特に最近は300Wを超える製品もありますので特に重要なポイントかと思います。

デメリットその1

VRMのフェーズ数を増やすと性能の向上が見込めるということは分かってきましたが、その一方でデメリットもあります。

まず上げられる点ですが、単純に駆動させるVRMの並列数を増やすと出力に現れる電圧リプルが大きくなってしまいます。

先程のマザーボードの例では12Vを1.2Vまで落とすと説明しましたが、このデューティ比が10%という動作条件はリプル成分が多く現れることになります。

ただ、これについては「インターリーブ制御」という方式を用いることでかなり低減させることができます。今回は自作の基板も作成しましたので、後ほど実験を交えながら解説します。

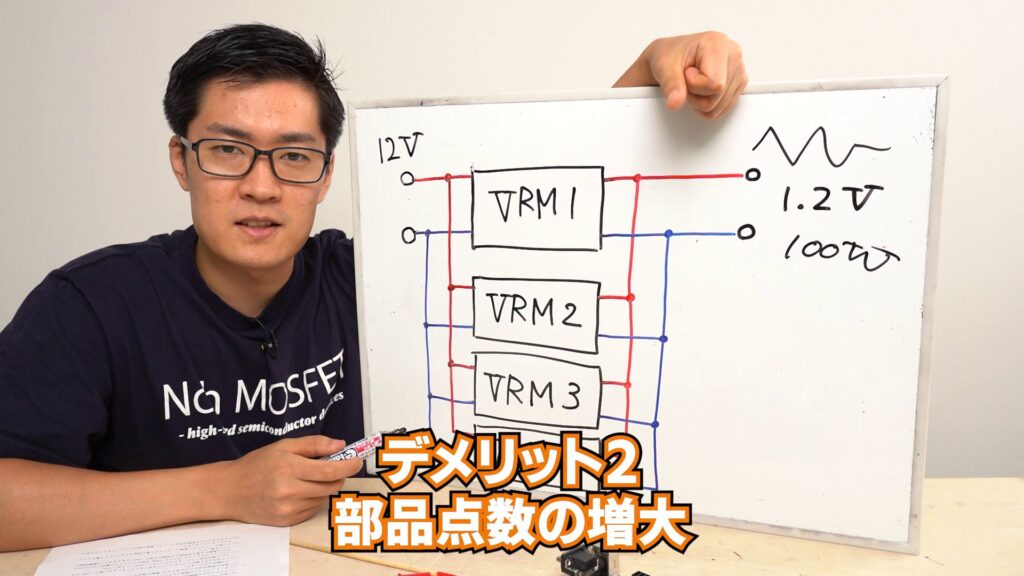

デメリットその2

デメリットの2つ目、部品点数の増大です。

当然のことではありますがフェーズ数が増えるとそれに伴って部品点数は増えてしまいます。1つのマザーボードに対して実装しなければいけない部品が多くなるということはそれだけコストもかかりますので、負荷が分散できる(定格の大きい高級な部品を使用しなくてもよい)一方で、トータルでのコストは上がってしまうことになります。

ただし、何度も触れているように、一つ一つの部品の定格を下げてより廉価な部品を使用することができますので、調達の観点からすると部品あたりの単価は下げられます。

ただし使用する部品についてはマザーボードメーカー各社によって味付けがかなり異なります。

フェーズ数の多いマザーボードはそれだけハイスペックな部品を使用するということで高級になる傾向があります。高級マザーボードの場合それぞれの部品にこだわりを見せることで商品の付加価値とする場合もありますので、なんだかんだ言ってフェーズ数の多さは高価格と結びつくのかもしれません。

デメリットその3

また、これは状況に左右されるものの、フェーズ数を増やしていくとマザーボード上に占めるVRM回路部分の専有面積も増えていくことになります。

今回サンプルとして購入したマザーボードでも(これが一般的な配置というのもあるかと思いますが)基板上部のそこそこの範囲に電源関係の部品を配置する必要が出てきています。

このように、VRMのフェーズ数を増やすことで性能的な恩恵が受けられるものの、コストとトレードオフの関係になっていることがわかりました。

VRM回路を自作してみる

実際のマザーボードから読み取ることができる解説はここまでにして、次にVRM(降圧コンバータ)と同じものを自作してみましたので、こちらを用いて実験と解説をしていきたいと思います。

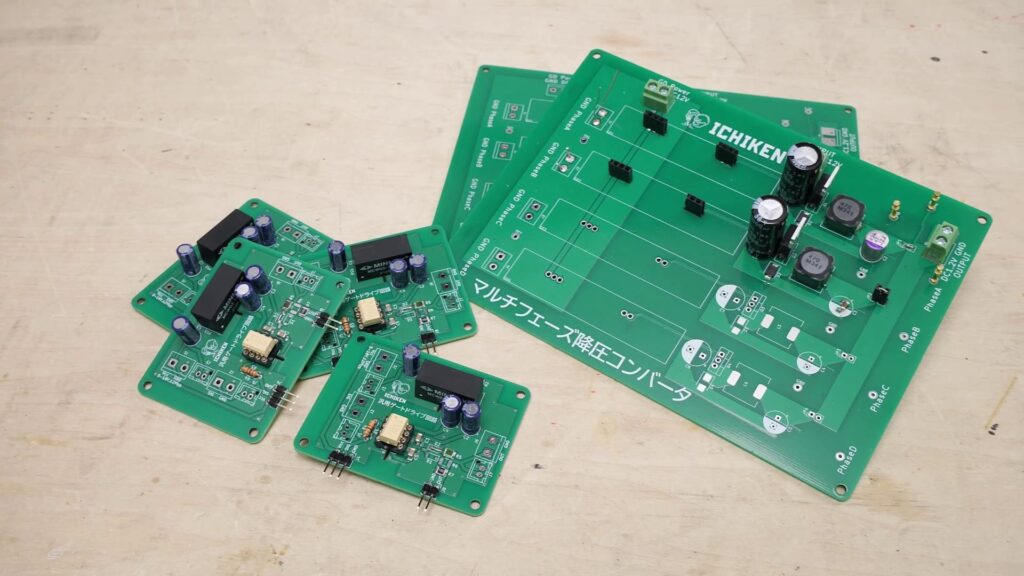

ちなみに今回も基板の製造はJLCPCBに発注しました。

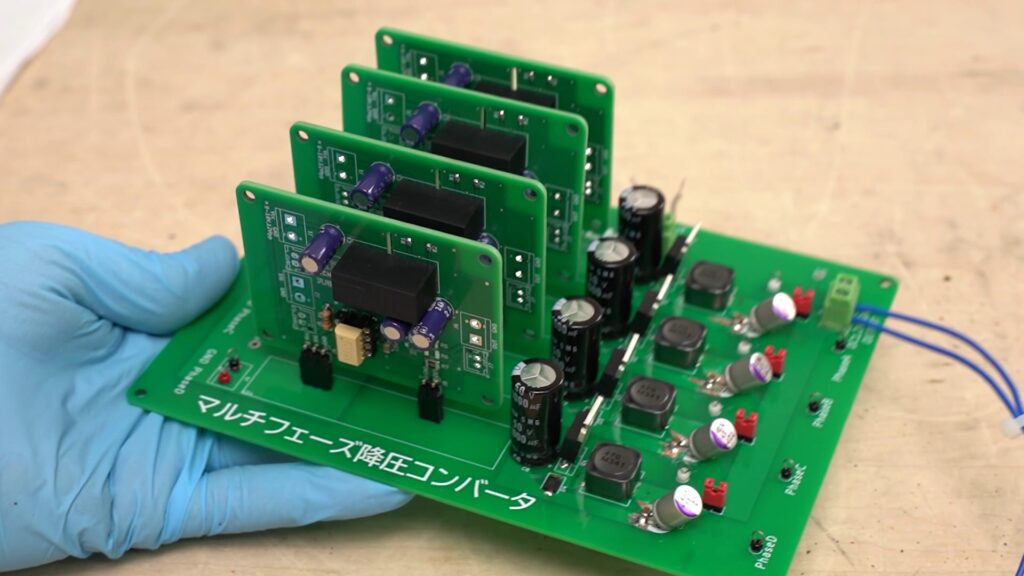

今回作った基板について

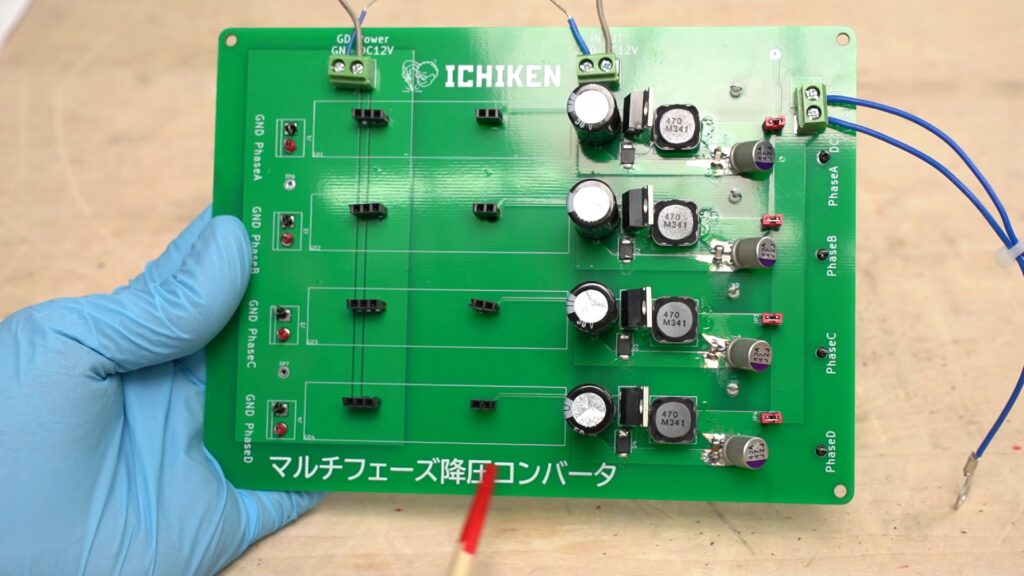

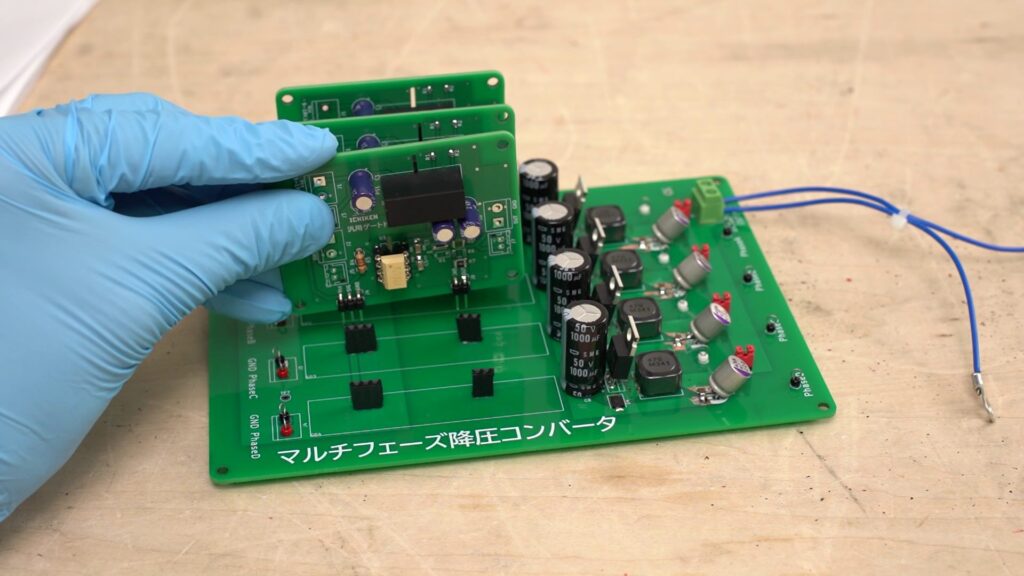

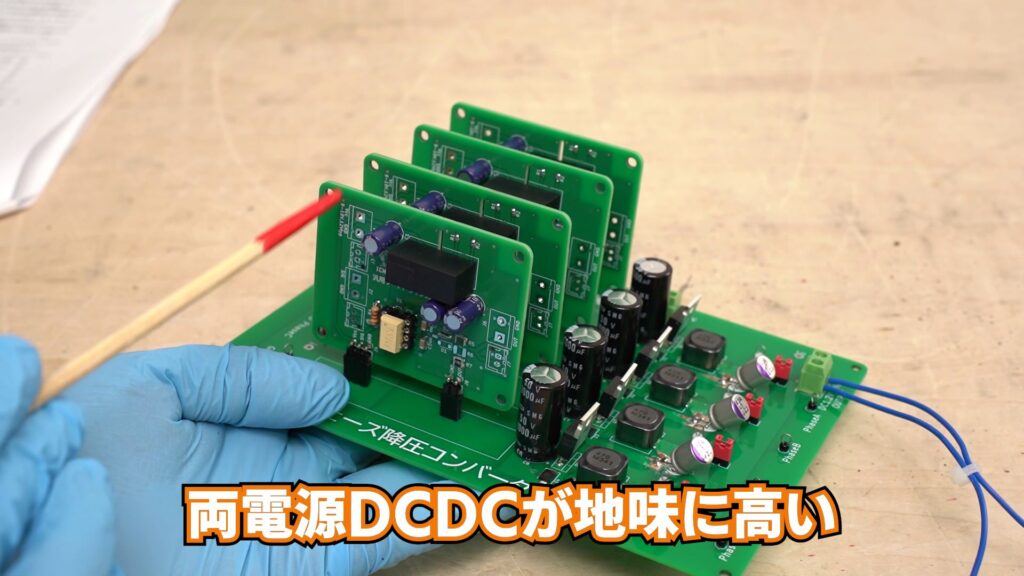

今回は降圧コンバータを複数並列にした動作を確認するため、4並列(4フェーズ分)を一枚の基板に収めた基板を設計しました。「マルチフェーズ降圧コンバータ基板」です。

全く同じ降圧コンバータ回路が4列並んでおり、それぞれがVRMのフェーズ1から4として動作します。基板上には降圧コンバータ部分の回路しか作っていないので、動作用の信号入力にはファンクションジェネレータを接続します。

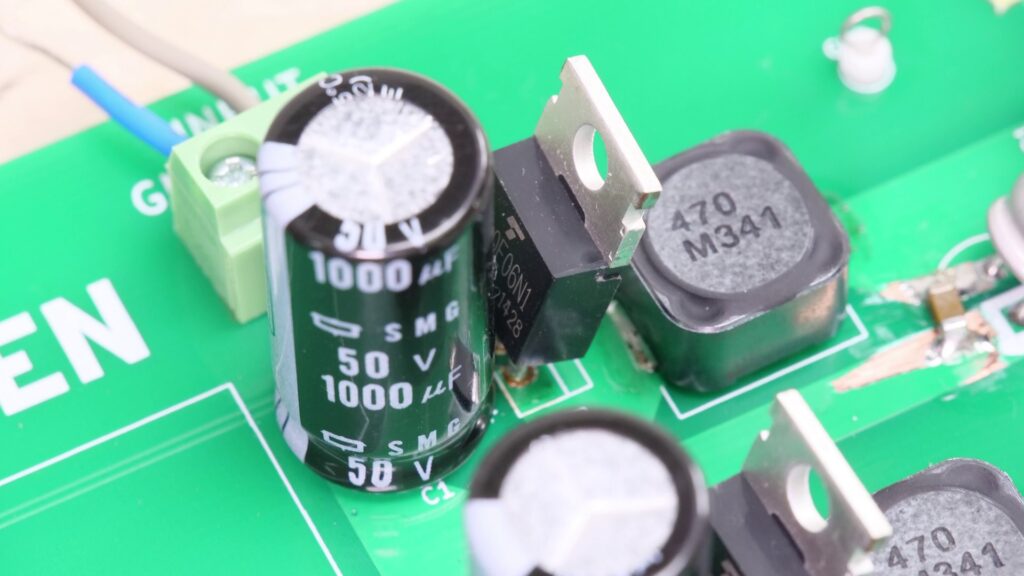

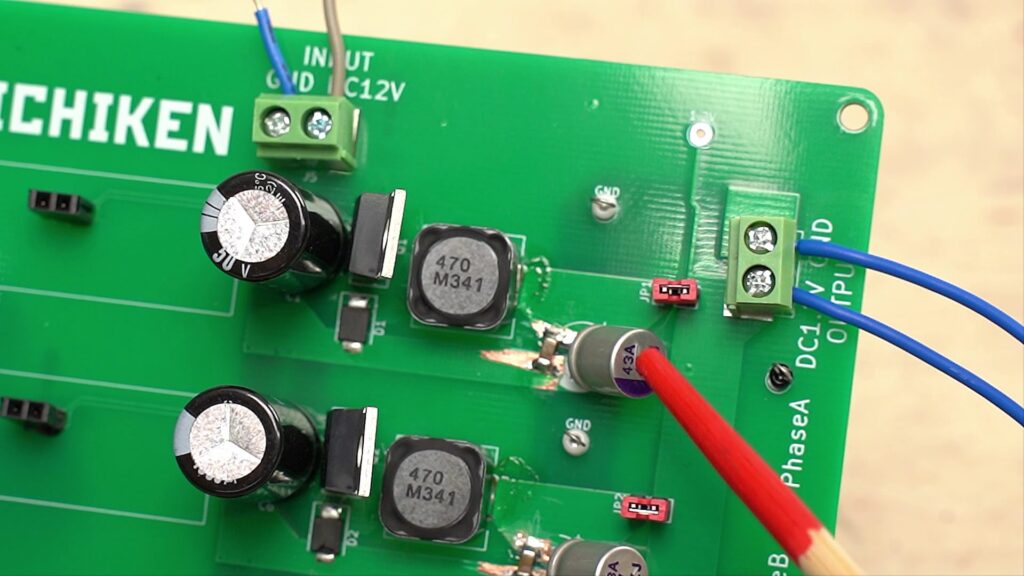

基板上の回路をざっくりと説明すると、まず入力側の電解コンデンサと上側のスイッチの役割をするNch-MOSFETが実装されています。

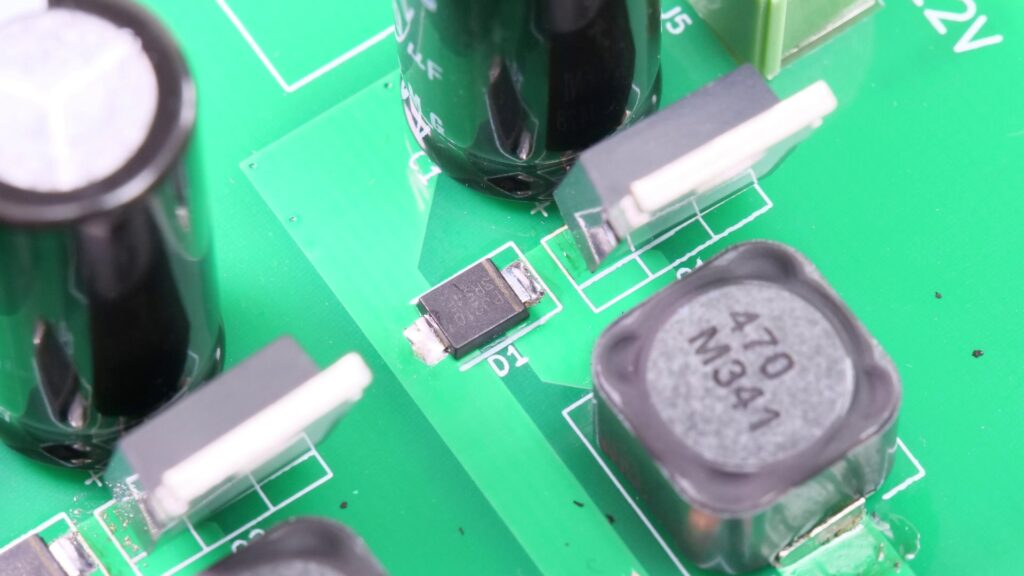

下側のスイッチはMOSFETを使用せずにショットキーバリアダイオードを使用しました。実は降圧コンバータの回路においてはスイッチが上下とも開閉できる必要はなく、下側のスイッチについては(順方向電圧降下を無視できる限りは)ダイオードでも動作させることができます。

降圧コンバータ部分右側にはインダクタと出力側電解コンデンサが実装されています。今回は導電性高分子アルミ固体コンデンサと補機としてチップコンデンサを実装しています。

こちらの基板、降圧コンバータについては4回路分作り込まれているのですがこの状態では駆動させることができず、MOSFETのドライブ用のゲートドライブ回路を接続する必要があります。

ゲートドライブ回路については他のプロジェクトでも使いまわしができるよう別の小型の基板に作り込んで、降圧コンバータ基板に対して差し込めるような形状で製作しています。

実際の所ゲートドライブ回路に実装している部品のほうが単価が高く、だいたい一回路あたり1500円前後の部品を実装する必要があります。マルチフェーズ降圧コンバータ基板にそれらを複数セット実装するのを避けたかったので今回このような制作手法を採用したわけですが、すべて組み合わせた状態の見た目がかっこいいので正直気に入っています。

フェーズ数の違いを比較(発熱)

さて、自作のマルチフェーズVRMも完成しましたので、まずはフェーズ数の違いでどの程度発熱に差が現れるかの実験をしていきます。

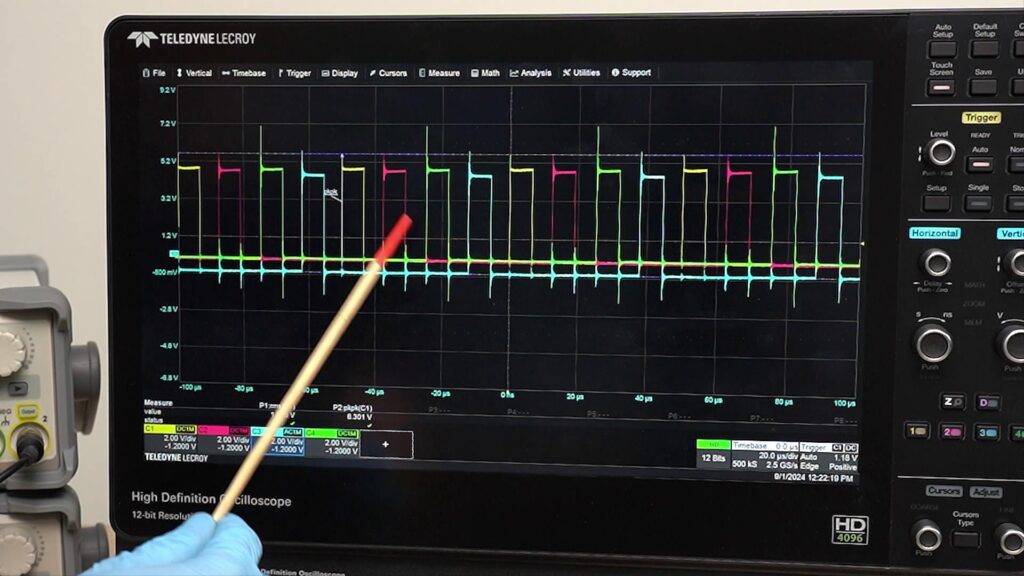

オシロスコープ上でそれぞれの4フェーズ分の入力波形を監視しています。1から4フェーズまで問題なく動作しています。

が、正直わかりづらいので気になる方は動画の方から確認していただけると幸いです。

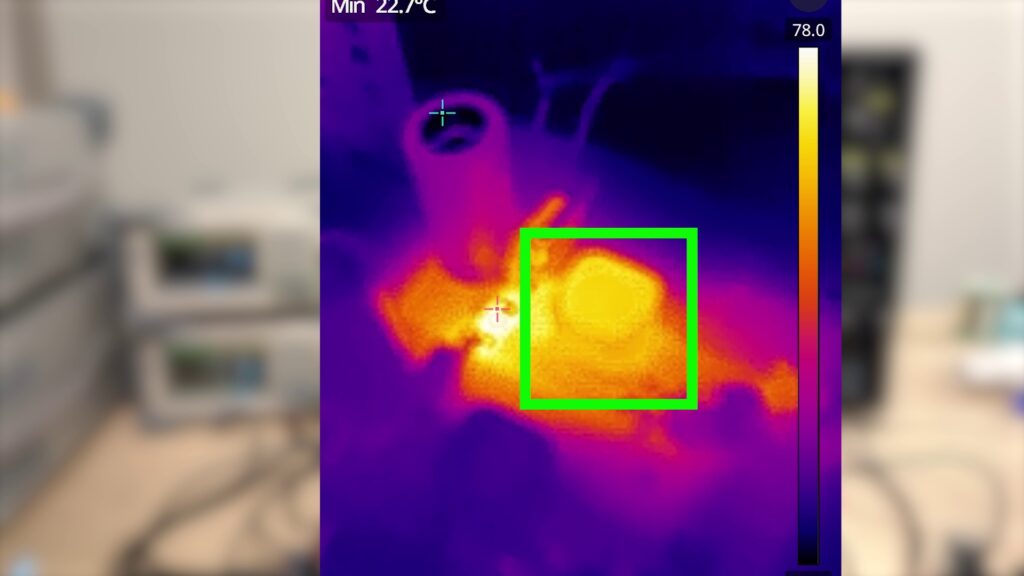

1フェーズ動作時の発熱

まずは4つのうち1フェーズだけを動作させている状態の発熱を確認してみます。

この状態ですと1つのVRMがすべての電力を負担している状態です。発熱は最大で70℃台後半になりました。今回の回路では特に部品に対して放熱対策はしていません。

ちなみに一番発熱しているのはショットキーバリアダイオードで、次点でインダクタの発熱がかなり酷いという状況になっています。特にインダクタについては常に電力が流れているわけですので、それだけ発熱しやすい部品となります。

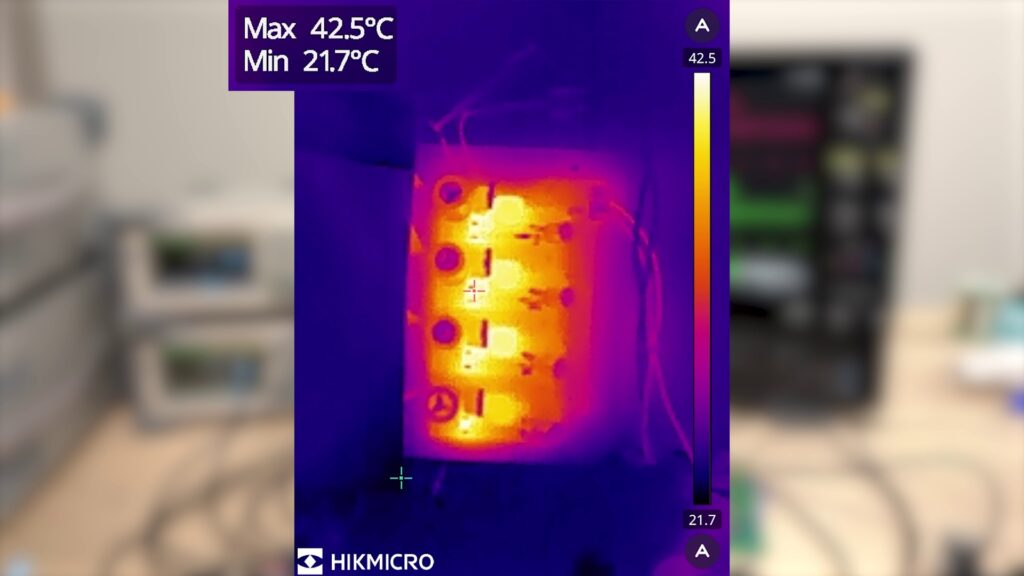

4フェーズ動作時はどうか

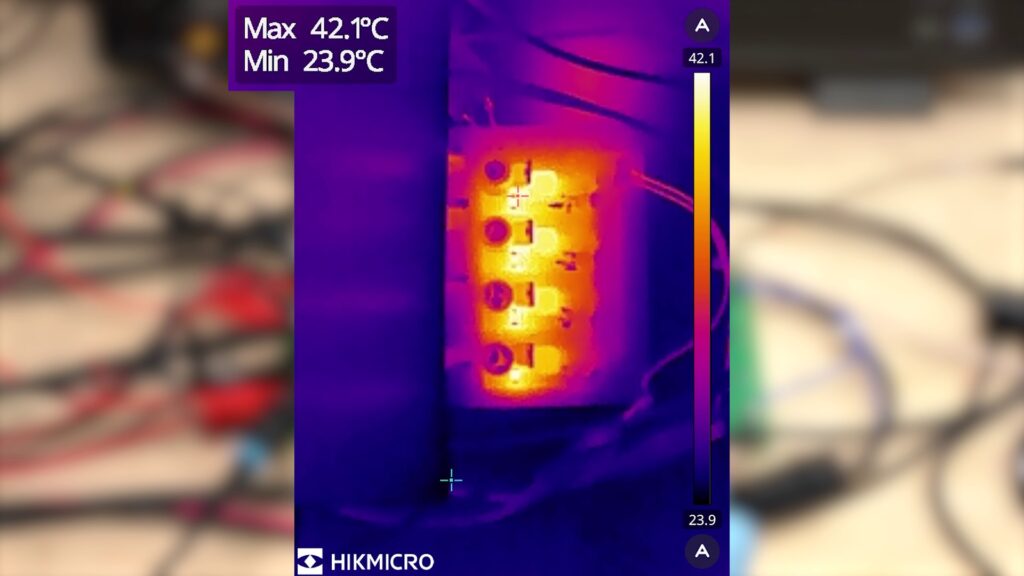

次に入力信号を4フェーズ全てに与えて4フェーズで同じ動作をさせてみました。この状態での発熱はだいたい42℃程度で、4つのVRMがほぼ均等に発熱しているような状態です。

複数のVRMを並列に接続することでそれぞれのVRM回路あたりの負荷が減った結果、発熱を抑えることができました。今回はシステム全体としての損失や発熱量については測定していませんので発熱の総量は不明なものの、それでもそれぞれの部品の最高発熱温度を30℃以上低下させることができています。

フェーズ数の違いを比較

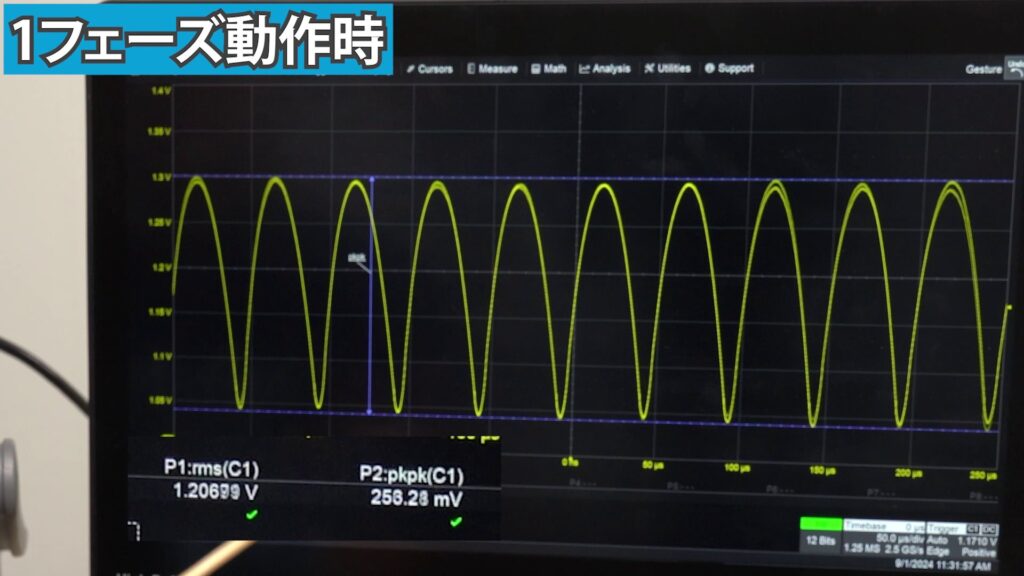

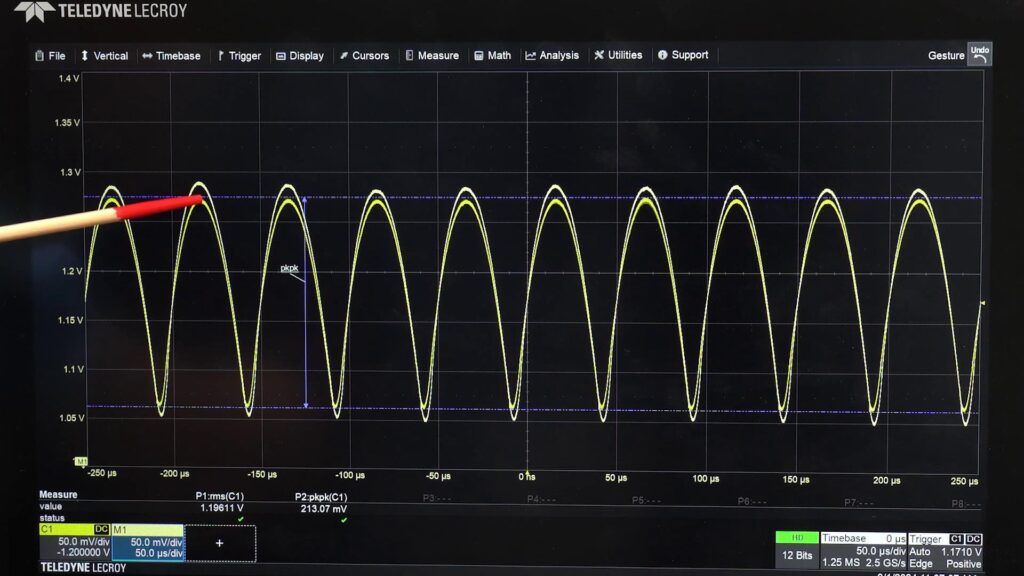

マルチフェーズ動作時の出力電圧波形もオシロスコープで見てみます。

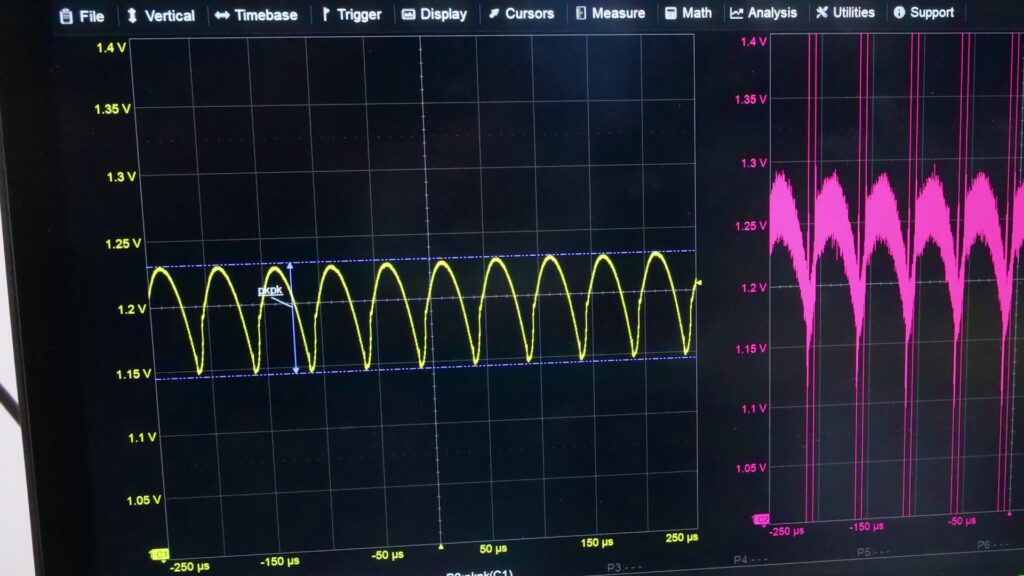

先程説明したようにデューティ比が10%で動作している状態ですので出力側にもそこそこのリプル電圧が見えています。ピークピークの振幅で250mVと結構大きい印象です。

ちなみに今回のマルチフェーズ降圧コンバータは設計段階であまり電圧リプルに対して対策するような設計手法は取っていません。これは基本的な回路で作成することで、マルチフェーズ動作時の挙動を比較しやすくするためです。

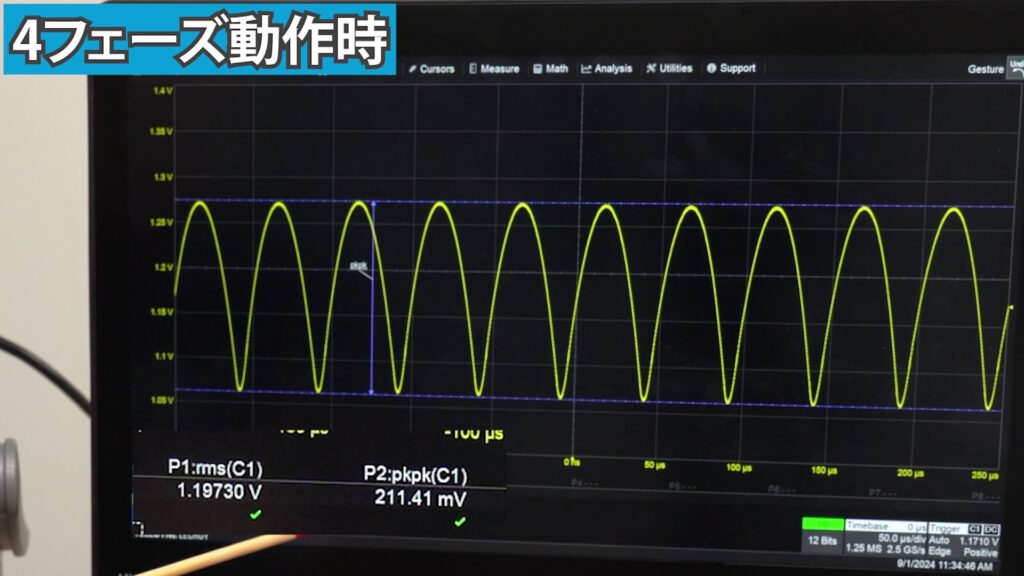

動作しているVRMを4つに増やした状態の出力電圧波形がこちらの画像です。

入力と出力の設定については変わらず12Vを1.2Vにするデューティ比10%の状態です。先程の1フェーズ動作時とくらべて電圧リプル波形に変化はなく、ピークピークで210mVと、40mV程度の低減効果は見られましたがあまり効果はないようです。

1フェーズ動作時の波形と4フェーズ動作時の波形を重ねて表示するとこのようになります。ここまでの実験で、

- フェーズ数を増やすことにより1つあたりにのVRMの負担≒発熱は低減する

- フェーズ数を増やしても、出力電圧の電圧リプルはあまり変わらない

という結果になりました。この実験結果ではマルチフェーズ化によって出力電圧の品質は向上しないように見えますが、しかしとある手法を用いることで劇的に変化させる事ができてしまいます。

出力の電圧リプルを減らす方法とは

マルチフェーズ化しても特に変化のなかった出力電圧リプルについて、実はVRMの制御方式を変えることで、回路の構成はそのままに大幅に低減することができます。

先ほども登場しましたが、「インターリーブ制御」と呼ばれるものです。ここからはその制御方法について解説します。

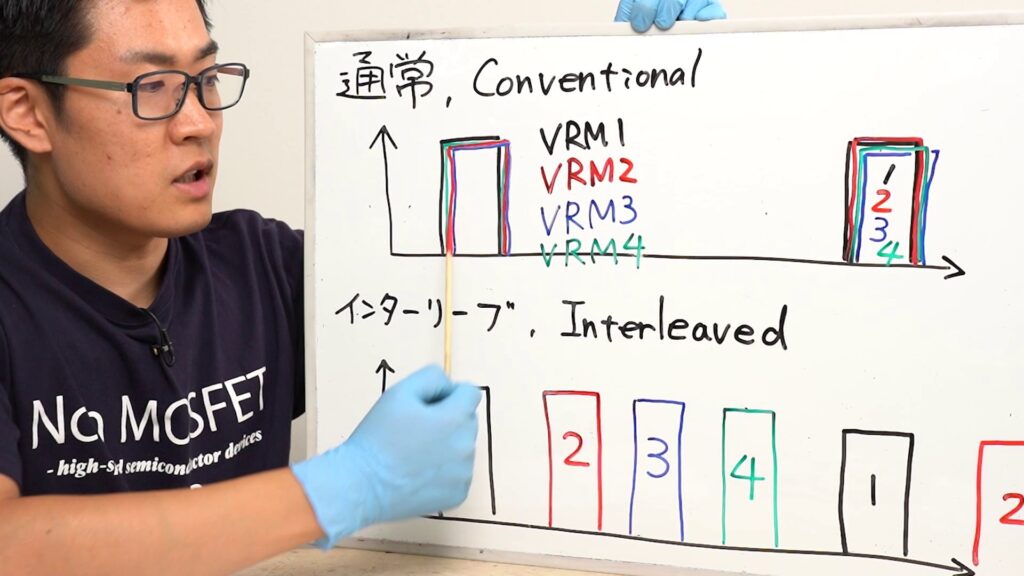

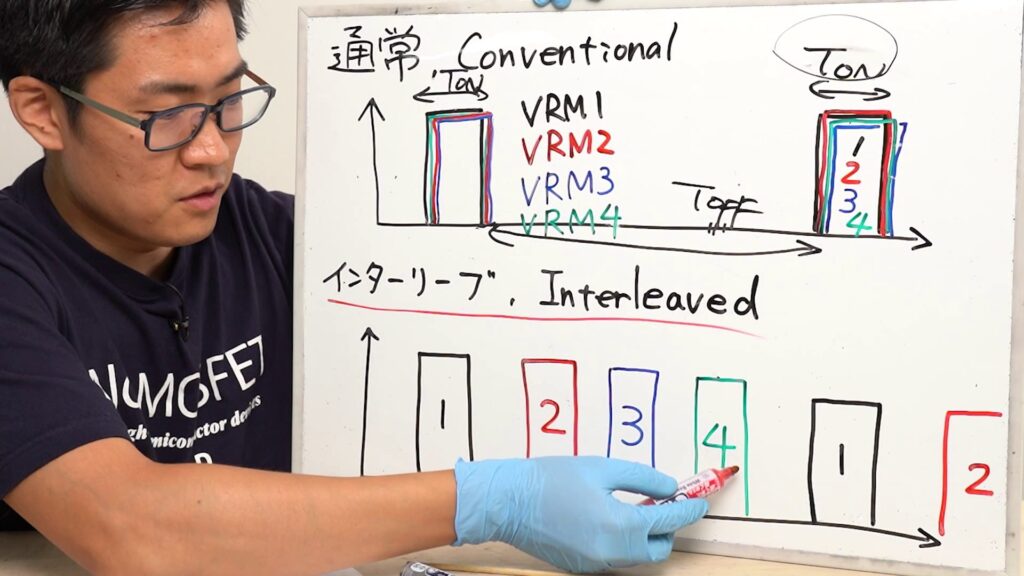

ここまで使用していた制御方式

ここまでの実験で自作のマルチフェーズ降圧コンバータを駆動していた制御方式が、こちらのホワイトボード上側の制御方式です。

グラフの横軸は時間で、その時間経過に対してどのタイミングでVRMが動作するか(MOSFETをスイッチングさせるか)を表しており、現状はVRM1からVRM4までのスイッチがすべて同時に動作している状態です。T-onは全体(1サイクル)あたり10%の時間になります。

T-offの時間はインダクタと出力側電解コンデンサのみからエネルギー供給をしている状態ですので、言い換えると12VのATX電源から電力を供給している時間は10%しかないことになりますので、これでは出力の電圧波形もなかなか安定させることができず、電圧リプルがどうしても大きくなってしまいます。

通常の制御のまま電圧リプルを減らす方法

こちらのすべてのVRMに対して同じ制御信号を与えて動作させるような制御方式のまま電圧リプルを減らそうとした場合、T-offの期間に供給できるエネルギーを増やせばいいわけですので、

- インダクタを大きくする

- 電解コンデンサを大きくする

- スイッチング周波数を高くする

などの対処法が考えられます。

ただし部品を大きくするといっても回路規模の時に述べたように、マザーボード上に実装できる部品のサイズには制約があり際限なく大きくすることができませんし、スイッチング周波数も際限なく高くできるわけではありません。

また、スイッチング周波数を上げようにも、そもそもスイッチングレギュレーターでは半導体のスイッチング損失が発熱の要因の一つとして存在します。このスイッチング損失は出力の切り替えの回数が増えれば増えるほど大きくなるわけですので、全体の損失が増えることになってしまいます。

放熱の限界もありますのでスイッチング周波数を上げるというのもやはり制約が伴います。

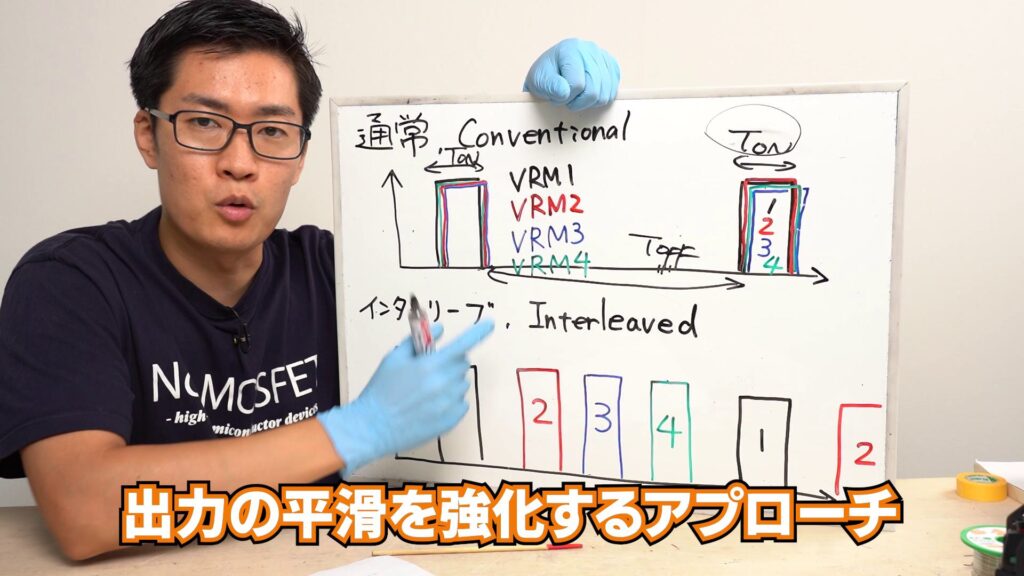

インターリーブ制御を用いる

ここからが本題の、制御方式によって電圧リプルを減らす「インターリーブ制御」の解説です。

インターリーブ制御の仕組みですが、すべてのVRMを同時に動作させるのではなくて、それぞれのT-onしているタイミングを適切にずらすことで電圧リプルをかなり効果的に減らすことができるようになります。

- 1フェーズ目のVRMがオン → オフ

- 2フェーズ目のVRMがオン → オフ

- 3フェーズ目のVRMがオン → オフ

- 4フェーズ目のVRMがオン → オフ

- 1フェーズ目のVRMがオン → オフ

- 2フェーズ目のVRMがオン → オフ

- 以降繰り返し

といったような形で動作させるわけです。

今回イチケンで自作した回路ではVRMのフェーズ数は4でしたが、これをたとえば10フェーズに増やしたと想定してみます。

このときデューティ比が10%で動作しているものが10個あると常にどこかしらのVRMが電力を供給していることになりますので、電力リプルを非常に少なくすることができます。

波形を見てみる

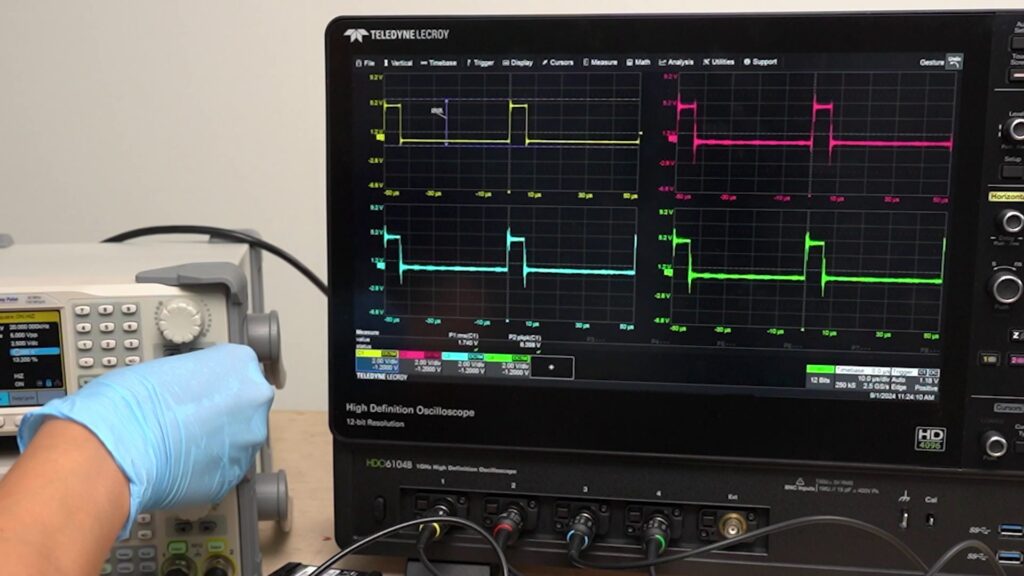

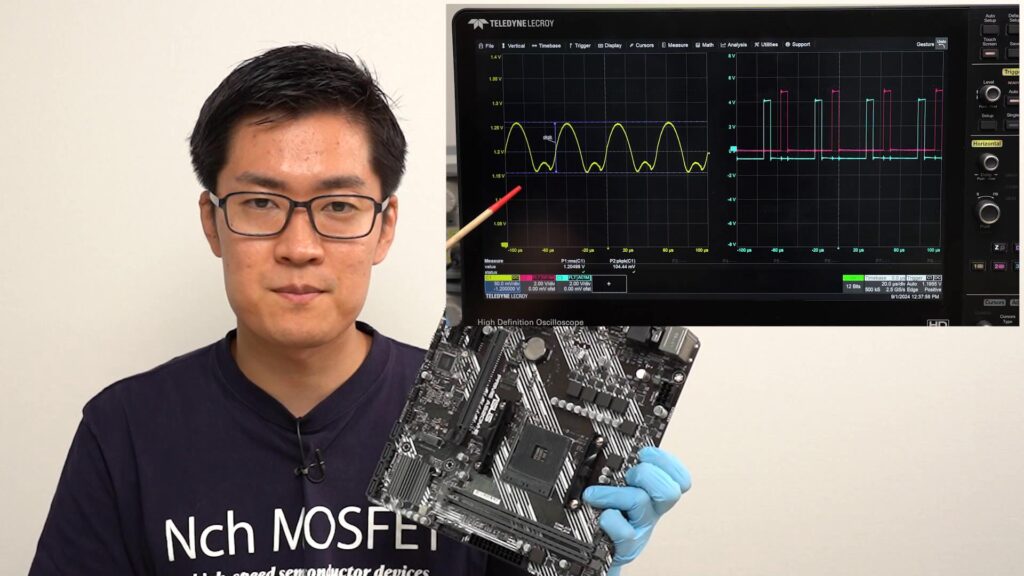

従来方式とインターリーブ制御制御時の電圧リプルの低減効果について、オシロスコープで確認していきたいと思います。制御用の入力信号ですが、すべてのVRMが重複しないタイミングで動作していることが分かるかと思います。

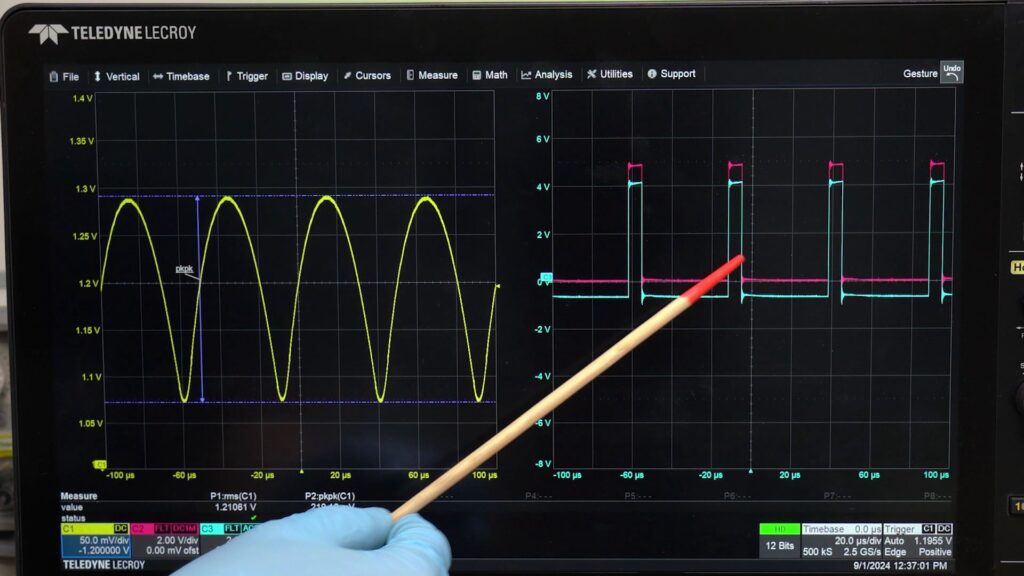

まずはインターリーブ制御の効果を確認するため、2つのVRMが動作している状態を作ってみます。最初の状態では2つのVRMは同じタイミングでスイッチングをしていますが、タイミング(位相)を10°ずつズラしていくとこのように出力に現れていた電圧リプルの波形が分割されるような形で変化することがわかります。

最終的に位相を180°ずらした状態だとこのような出力となり、同期して動作していた時にはピークピークで220mV程度あった電圧リプルが48mVまで低下しています。実に4分の1以下と、かなり大きな低減効果です。

動作しているフェーズ数を4つに増やした状態でもインターリーブ制御をしてみました。それぞれの制御信号は90°ズレている状態です

4フェーズでインターリーブ制御させたとき、ほとんど電圧リプル波形を確認することができなくなってしまいました。縦軸を拡大してピークピークの電圧リプルを確認してみると、12mVと相当減っていることがわかります。

4つのフェーズをすべて同時に動作させていたときには220mVほどあったものが、それぞれの動作タイミングをずらすだけで12mVと約20分の1ほどまで低下したことになりますので、かなりの電圧リプル低減効果があるようです。

発熱はどうか

ちなみに電圧リプルについては大きな低減効果があった一方で、温度変化はあまりありません。

実測で(一番発熱している箇所で)42℃程度と、発熱の低減効果はほとんど期待できないようです。動作のタイミングはバラけても、単位時間あたりの出力の負荷が変わっていない≒コンバータ全体で負担する損失は変わっていないためです。

使用した機材について

ちなみに今回出力電圧リプルの測定を行うにあたって、オシロスコープには受動プローブではなく電源レールプローブを接続して波形を測定しています。

というのも受動プローブを使用すると純粋な出力波形を測定することが難しく、真の波形からだいぶ変化した波形を観測することになっていまいます。実際に電源レールプローブと受動プローブでの測定波形を比較してみるとこのような感じです。

電源レールプロープの使用、また、出力部分のカップリングなどかなり気を使った測定をすることで、今回はかなりきれいな状態の出力電圧波形を測定することができました。今回使用したテレダイン・レクロイの電源レールプローブが気になる方は、是非以下のリンクから確認してみてください。

今回のまとめ

というわけで今回はマザーボードのVRM・電源フェーズ数について、その理論と自作のマルチフェーズ降圧コンバータを用いて解説をしてきました。

フェーズ数が多くなると1フェーズあたりの負担する電力が少なくなり、システム全体では大電力への対応や発熱の分散と言った効果が見込めることがわかりました。

また、それぞれのフェーズをタイミングをずらして動作させる「インターリーブ制御」を用いて駆動することで、回路構成や部品実装に全く変更を加えることなく、出力の電圧の品質を向上させる事ができます。

昨今はCPUの消費電力も(制限をかけないかぎり)100Wから300Wとかなり大きくなっています。ですのでそういった大電力への対応かつ品質の良い電力供給のためには、VRMのフェーズ数が多いマザーボードが有利だという事が言えるでしょう。

今回の解説については既にYouTubeで動画も公開しています。制御方式の解説を実況形式で見たい方など、是非こちらもあわせてご覧いただけますと大変幸いです。

それでは今回も最後までお付き合いいただき誠にありがとうございました。

コメント

コメント一覧 (2件)

VRMについて勉強し始めたところなので表現が間違っていたらごめんなさい。

CPUの能力に対してVRMフェーズが多すぎることで何か不利なことはありますか?

フェーズ数が多いと無駄が増えて消費電力が増加します。その代わり安定性が向上します。

多くのマザーボードではファームウェアの制御で低負荷時にスイッチング周波数やフェーズ数を動的に下げることで、アイドル時の効率が良くなるようにしています。

電圧下げ等をすると流れる電流が少なくなる為、更にフェーズ数やスイッチング周波数が下がりやすくなり安定性が悪化します。(リプルノイズが増加します)

メーカーによってはスイッチング周波数やフェーズ数をBIOS設定で変更出来るものがあります。

例えばMSIやASUSのミドル~ハイエンドのマザーボードですね。

これらの製品は低負荷時であってもスイッチング周波数やフェーズ数を減らさないように設定することが出来ます。

これにより電圧下げを行っていてもアイドル時の安定性が向上するので、

負荷テストは通るのにアイドル時にいきなり青画面になる、というような事が少なくなります。

スイッチング周波数やフェーズ数が安定性に影響するのはこの記事を読めば理解出来ると思います。

尚、ASRockやBIOSTARは上記の設定がBIOSに無いので、残念ながら電圧下げにはあまり向いていません。

フェーズ数だけは多いのでOC方面(電圧を上げる方)なら使えます。

例えば、スイッチング周波数が250KHzと1000KHzでは、CPUの安定性に必要な電圧が0.05~0.1v違って来たりというような事もあります。

オート設定の場合、効率重視か安定性重視かでこの辺のチューニングは違って来るので、

同じレギュレータ、同じフェーズ数のマザーボードであっても、単純に消費電力が少ないマザーボードが高性能とはなりません。

マザーボードを比較する場合、効率(消費電力)だけ見てもダメで安定性も比較しないと意味はありません。

ATX電源でも効率は良いがスイッチング周波数が低くて電圧ブレブレな製品があるのと同じです。

負荷変動に対して過渡応答が遅いと効率(消費電力)は良くても電圧変動に弱くなってしまうのです。